JOURNAL

FPGAS. The New Matrix for Design

# PROCESSING CHOICES EXPAND FOR MILITARY APPS

Volume 8 Number 5 May 2006

www.cotsjournalonline.com

#### **PLUS:**

**Configurable Computing Solutions Ready to Take Off**

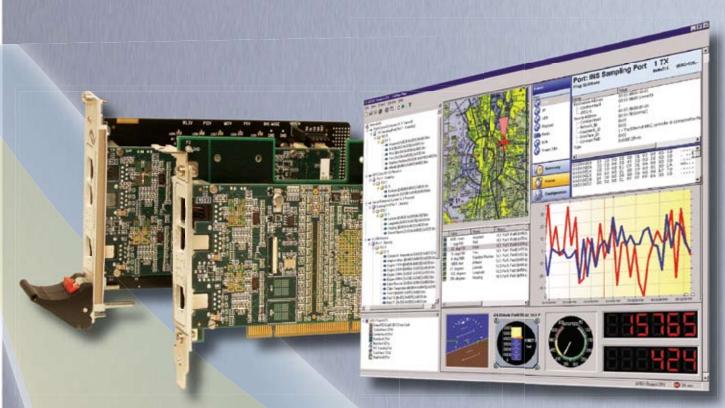

Tech Focus: FPDP/FPDP II Boards

#### Need reliability?

-40° to +85°

EPIC™ XE-900 I.0 GHz CPU

| Features        | XE-900                    | XE-800             | XE-700           |  |

|-----------------|---------------------------|--------------------|------------------|--|

| CPU             | Via Eden                  | AMD Geode GXI      | STPC             |  |

| Clock speed     | 400 MHz; 733 MHz; 1.0 GHz | 300 MHz            | 133 MHz          |  |

| BIOS            | General Software          | Phoenix            | Phoneix          |  |

| DRAM support    | to 256 MB                 | to 256 MB          | 32/64 MB         |  |

| Compact/Flash   | Type I or II              | Type I or II       | Type I or II     |  |

| COM I           | RS-232                    | RS-232/422/485     | RS-232           |  |

| COM 2           | RS-232                    | RS-232/422/485     | RS-232/422/485   |  |

| COM 3           | RS-232                    | NA                 | RS-422/485       |  |

| COM 4           | RS-232                    | NA                 | RS-232           |  |

| COM 5           | RS-232/422/485            | NA                 | NA               |  |

| COM 6           | RS-422/485/TTL            | NA                 | NA               |  |

| LPTI            | 0                         | 0                  | 1                |  |

| EIDE            | 2                         | 2                  | 1                |  |

| USB             | 2                         | 6                  | 2                |  |

| CRT             | 1600 × 1200               | 1280 × 1024        | 1280 × 1024      |  |

| Flat panel      | LVDS                      | yes                | yes              |  |

| Digital I/O     | 24-bit prog.              | 48-bit prog.       | 24-bit prog.     |  |

| Ethernet        | 10/100 Base-T             | Dual 10/100 Base-T | 10/100 Base-T    |  |

| Expansion       | PC/104 & Plus             | PC/104 & Plus      | PC/104           |  |

| Power           | 3.6A operating            | I.6A max.          | I.6A max         |  |

| Temp. range     | -40° to 70/85° C          | –40° to 80° C      | -40° to 80/85° C |  |

| Shock/vibration | 40/5g                     | 40/5g              | 40/5g            |  |

# Need Linux, QNX, Windows®? Try our OS EMBEDDER™ KITS

Our kits are the shortest path to a successful OS on an Octagon embedded computer.

- Pick your Octagon SBC

- Pick the OS you prefer: Linux, Windows, QNX

Octagon delivers a high performance, total solution.

#### Typical Linux kit includes:

- Target CPU card

- Preloaded OS image on 256 MB industrial CompactFlash

- 256 MB SO-DIMM module

- Interface cables

- Hard copy of manual

- Mouse

- CPU OS bootable CD

- Optimized OS version

- Full driver support for on—board hardware

- X-Windows support

- Example applications and source code

- Extra documentation

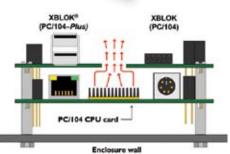

# Need PC/IO4 expansion? Try our XBLOKs®

**XBLOKs** offer the best compromise in cost and function for both PC/104 and PC/104-Plus. Only 44% the size of a standard PC/104 card, you can add two functions to your system but increase the stack height by only one level. —40° to 85° C. Heat diagram shows enhanced cooling.

#### X-SRAM-2 MB

- 2 MB high speed, SRAM

- · Read and write at full bus speed

- Pointers to memory saved if CPU resets or loses power

## X-DIO-48 bit programmable digital I/O

- 48 digital I/O, 5V compatible

- Source and sink 16 mA per output

- Direct connection to opto-module racks

#### X-COM-2 dual UART

- Up to 230.4 kBaud data rate

- Supports RS-232/422/485

- RS-485 fault protected to ±60V

#### X-LAN-I Ethernet LAN

- 10/100 Base—T, Intel 82551ER

- Fully plug-n-play

- High performance, PCI bus interface

#### X-USB-4 quad USB 2.0

- Speeds up to 480 mbps

- Mix and match USB 1.1 and 2.0

- Current-limited ports can supply 500 mA to external devices

# Need a fanless system? NEW CONDUCTION COOLING SYSTEM

Designed for the **XE-900**, our conduction cooling system eliminates a fan even at 1.0 GHz.

For a full listing of Octagon Systems products, visit us at

www.octagonsystems.com

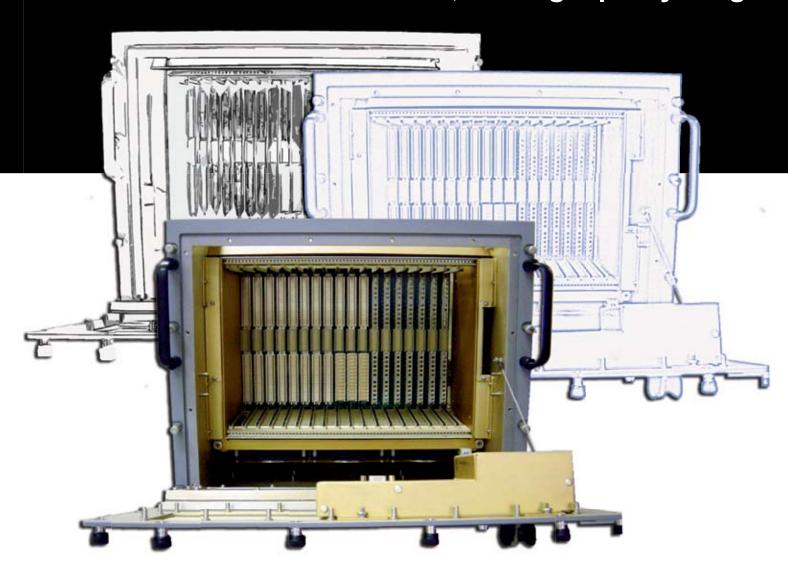

#### RC-1 SINGLE SLOT CHASSIS

6U VMEbus or cPCI rugged enclosure,

includes a built-in PMC site for I/O flexibility and safely dissipates over 80 W to free air.

www.cwcembedded.com/cha1

#### RC-2 AND RC-5 TWO AND FIVE SLOT CHASSIS

6U VMEbus or cPCI rugged system enclosures with a 28VDC power supply module and customizable front and rear I/O panels.

www.cwcembedded.com/cha1

#### LIQUID-COOLED CHASSIS

Cutting-edge technology, dissipates up to 450 W per slot!

www.cwcembedded.com/cha1

#### 1 ATR LONG SEVEN TO TEN SLOT CHASSIS

6U VMEbus or cPCI rugged system enclosure available in forced-air cooled cooling options.

#### 3/4 ATR FIVE SLOT CHASSIS

6U VEMbus or cPCI rugged system enclosure with 28VDC power supply module and forced-air cooling options.

www.cwcembedded.com/cha1

#### RcPCI 3U FIVE SLOT cPCI CHASSIS

Compact and powerful rugged system enclosure with forced-air cooling options, safely dissipates 130 W.

www.cwcembedded.com/cha1

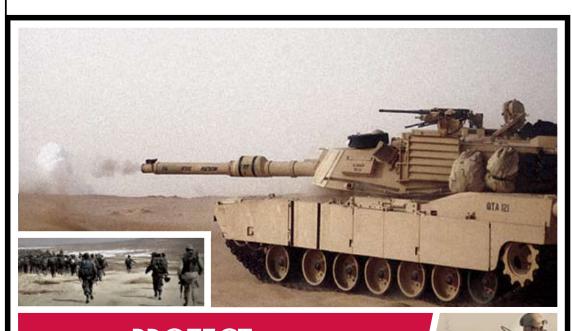

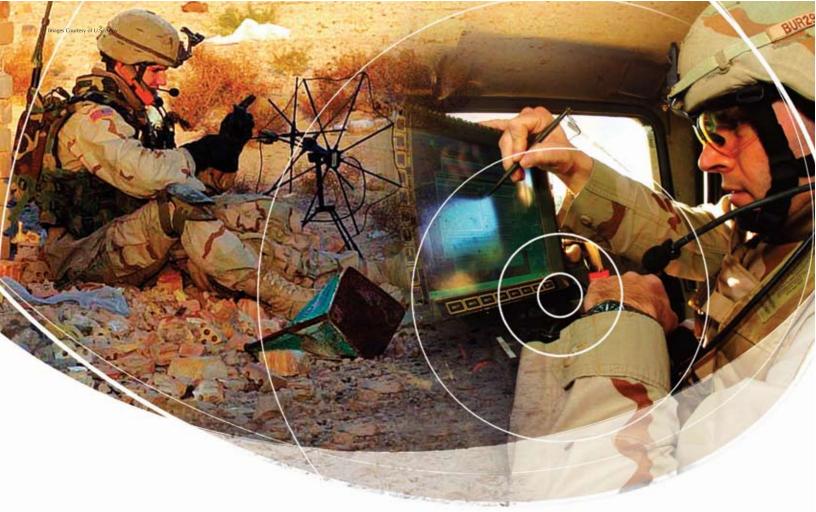

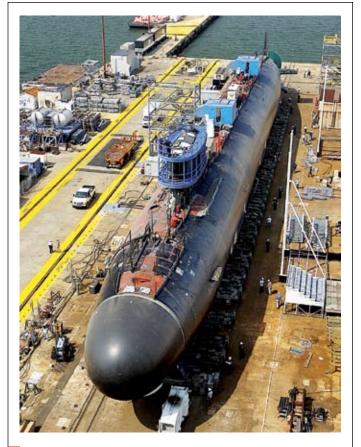

# OUR CHASSIS PROTECT MILITARY ELECTRONICS TO HELP PROTECTOUR TROOPS.

Modern military programs present a wide range of environmental and performance issues for system electronics. At Curtiss-Wright Controls Embedded Computing, we specialize in producing rugged enclosures which deliver steadfast electronics protection despite intense shock, vibration, corrosive atmospheres and severe temperatures. Curtiss-Wright battle-tested chassis help ensure the safety of our troops by providing reliable operation in the harshest environments.

Innovation In Motion

${\tt WWW.CWCEMBEDDED.COM}$

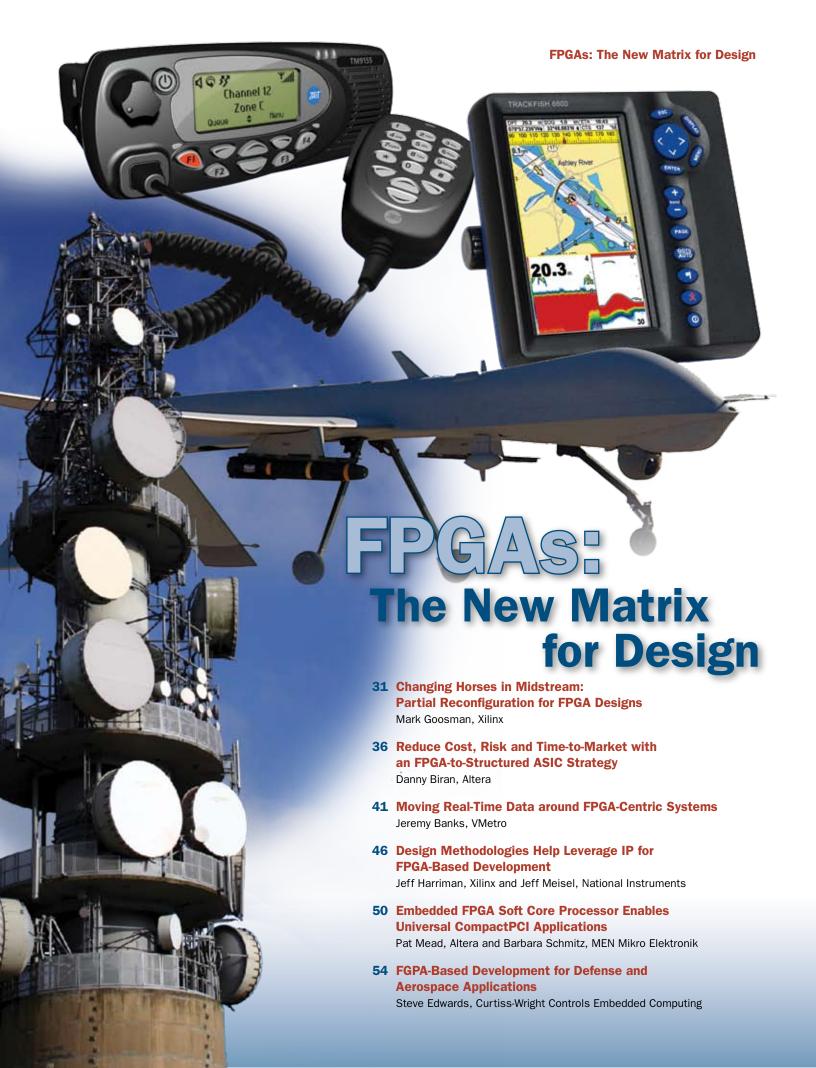

#### Main Feature

Tailoring Processors for Military Applications

- 16 Processors Combine Forces for Military Systems

Ann R. Thryft

- 21 Commercial Processors in Military Applications

Dawn Levy and Stephen Pearce, Mercury Computer Systems

#### Special Section

FPGAs: The New Matrix for Design

- 31 Changing Horses in Midstream: Partial Reconfiguration for FPGA Designs Mark Goosman, Xilinx

- Reduce Cost, Risk and Time-to-Market with an FPGA-to-Structured ASIC Strategy Danny Biran, Altera

- 41 Moving Real-Time Data around FPGA-Centric Systems

Jeremy Banks, VMetro

- **46** Design Methodologies Help Leverage IP for FPGA-Based Development Jeff Harriman, Xilinx and Jeff Meisel, National Instruments

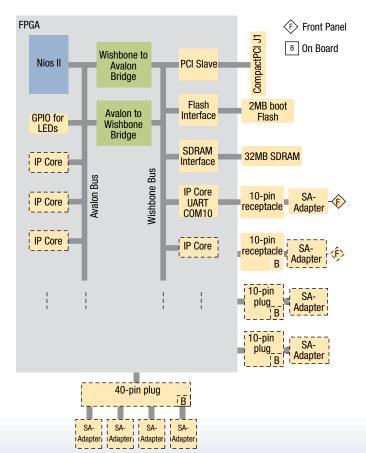

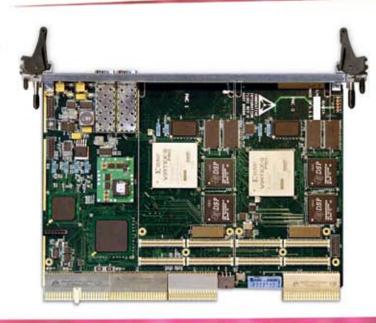

- Embedded FPGA Soft Core Processor Enables Universal CompactPCI Applications

Pat Mead, Altera and Barbara Schmitz, MEN Mikro Elektronik

- **54** FGPA-Based Development for Defense and Aerospace Applications Steve Edwards, Curtiss-Wright Controls Embedded Computing

#### Technology Focus

FPDP and FPDP II Boards

- Outside-the-Box Features Keep FPDP in the Game

Jeff Child

- **65** FPDP/FPDP II Boards Roundup

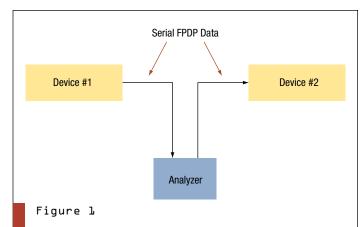

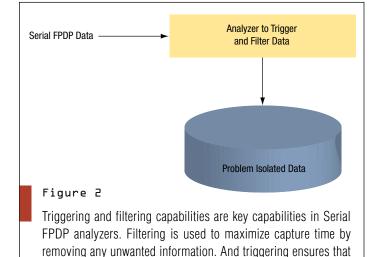

- 73 Effective Tools Smooth Serial FPDP Bus Analysis Task Nigel Brownlow and Roger Paje, Absolute Analysis

COTS (kots), n. 1. Commercial off-the-shelf. Terminology popularized in 1994 within U.S. DoD by SECDEF Wm. Perry's "Perry Memo" that changed military industry purchasing and design guidelines, making Mil-Specs acceptable only by waiver. COTS is generally defined for technology, goods and services as: a) using commercial business practices and specifications, b) not developed under government funding, c) offered for sale to the general market, d) still must meet the program ORD. 2. Commercial business practices include the accepted practice of customer-paid minor modification to standard COTS products to meet the customer's unique requirements.

——Ant. When applied to the procurement of electronics for the U.S. Military, COTS is a procurement philosophy and does not imply commercial, office environment or any other durability grade. E.g., rad-hard components designed and offered for sale to the general market are COTS if they were developed by the company and not under government funding.

#### Departments

6 .....Publisher's Notebook

11 .....The Inside Track

**78.....COTS Products**

86 ....Editorial

Calling all Robot Makers

Coming in June...

...See Page 85

computing, networking and display systems.

# Publisher's Notebook

always get into trouble when I try to write about technology, even if it's only from a marketing viewpoint. Perhaps my age and gender dictate that although I know I shouldn't, I can't keep myself from doing it anyway. Twenty-five years ago I was probably much more naive or ignorant of what was going on

# VME Skyrockets

than today. Back then there were only four open bus architectures—although "open" is a matter of interpretation—Multibus I, Multibus II, VERSAbus and VMEbus. I won't rehash old news, but fast-forward to today and VMEbus is still with us while the rest are in museums.

Today, I can't count the number of buses: some based on the PCI architecture, a slew of serial/switched fabrics, VME and its variants and so on. Note that I'm using a very generic interpretation of the term bus: a vehicle over which more than one electronic element exchanges data with another. There must be hundreds of buses if you count all the variants. I remember when Futurebus was talked about as being the "upgrade" path for all VME and Multibus users. It never came out of the incubator because there were too many variants in the Futurebus spec, and none of the variants developed a "critical mass" in the marketplace. How is it then that we have so many different bus architectures in existence today and so many companies that aren't going bankrupt?

Probably the primary answer to this question is that the embedded computer marketplace is much larger than it was fifteen years ago. And it continues to grow at an enormous rate. As a result, each of these technologies can grow large enough to sustain a small number of suppliers. Meanwhile, each of these buses provides sufficient diversity from the other to attract and keep a critical mass of users. These users are then nurtured by the suppliers through the addition of upgrade paths—upgrade paths that include some way to retain the user's investment. In my mind's eye, I picture the life cycle of a bus as a Fourth of July fireworks skyrocket. It shoots out, breaks into different paths, then each of those produces paths. Then, eventually, it fades and is gone.

Depending on what you've used and what interests you, every one of us has a different opinion of the bus architectures on the scene today. For shear tenacity the VMEbus has to be the most durable with a life line that as of this year stretches back twenty-five years. To what does VME—as it's now called—attribute its success? Well, like most things, luck and timing are

the biggest factors. If it wasn't for its success in penetrating the military market, VME would only be an afterthought in today's market. Why did VME become the darling of the military? Several reasons: form-factor, durability, a history, large supplier base, wide array of available products and backward compatibility. But timing and luck came into play in that VME had all those things just when the military was moving to accept open standards and systems. It wasn't leading-edge performance or technology that interested the military. In fact, as the military was getting interested in VME, the rest of the world was getting itchy to move away from it to design products based on other architectures.

So, just what is VME's future? We have a whole host of VITA 40 series numbers in the VSO cranking out variations of VME. Some offer a lot of backward compatibility, some very little. Each variant is designed to solve or complicate a market need, while trying to preserve some portion of a user's prior investment in VME.

Each time a new bus architecture is being presented to the market, I get the feeling like Moses is coming off the mountain carrying tablets. I've seen a lot of these trips, and most recently it's been VITA 58. I don't fully understand it, but I'm supposed to get a complete sermon at MEECC. The initial information is that there will no longer be connector issues, nor bus architecture issues; everything will be inside a metal can and you will pull one out and replace it with the same type or a different type.

The reason we have boards and buses is to have the ability to "configure" what we need. Most of us are old enough to realize that every ten years we go through a cycle where pundits proclaim that boards/modules will become obsolete because everything will be put on silicon. Yes, we do continue to put more on silicon, then we take those denser chunks of silicon and put them on boards or modules and the modules into systems, and the beat goes on. Until we get to a level of integration where we can put every conceivable electronic function necessary to run something like a tank in one module named "tank," and only insert or remove this one module, then we'll need to have electronic subsystems. How those subsystems are divided and what they will contain will evolve and change over time. Maybe VITA 58 solves all that and we will finally see the light go out on the VME skyrockets.

Pete Yeatman, Publisher COTS Journal

#### GF Fanuc Automation

### World-Class Solutions for World-Class Challenges

When the time comes to put your trust in a technology partner for the world's most demanding military applications, put your trust in GE Fanuc Embedded Systems. With GE Fanuc as your partner, you'll be teaming with an industry leader with a long and successful history of providing the military market with world-class solutions for world-class challenges.

GE Fanuc can quickly and effectively deliver a customized application for your specific requirements. We can also provide an off the shelf portfolio of SBCs, switches, controllers, rugged flat panel monitors and PCs, networking devices and much more, to meet your wide range of embedded computing needs. When the choice means this much, choose GE Fanuc.

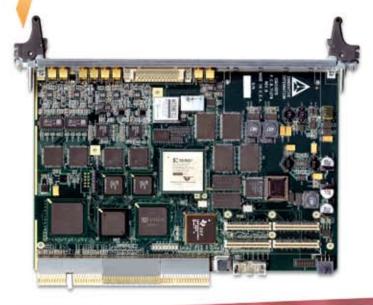

#### VME-7807 Intel® Pentium M VME Single Slot Single Board Computer

- VITA 31.1

- Processor speeds up to 1.8 GHz

- Up to 1.5 GB DDR SDRAM

- 64-bit, 66 MHz PCI-X PMC site

- Dual 10/100/1000 Ethernet

- 10/100 Ethernet

- Four 16550-compatible serial ports

- Four USB 2.0 ports

- $\bullet$  SVGA support on the front panel

- Serial ATA interface

- Up to 1 GB CompactFlash

#### RM921 VME Managed Gigabit Ethernet Switch with IPv6

- IPv6 support

- Layer 2/3/4 switching

- Twelve and twenty-four 10/100/1000 Ethernet port (front panel) options

- Copper and fiber connection options

- Full management support

- 802.1p, 802.1Q VLAN, deep packet filtering, link aggregation, Rapid Spanning Tree (802.1w, 802.1d), broadcast storm Control, port mirroring

#### VME-5565 Ultrahigh Speed Fiber Optic Reflective Memory with Interrupts

- Available in PMC, PCI, and VME form factors

- Easy-to-use shared memory networkoperating at 2.12 Gbaud

- Low latency for real-time applications

- Network transfer rates up to 174 Mbute/s

- Data connections up to 10 km (single-mode fiber)

- DMA controller

- Operating system and architecture independent

- Ultra low CPU overhead, onboard hardware manages communication protocol

#### Sentinel Ruggedized Flat Panel Monitor

- 10.4, 15, 19, and 21 inch AMTFT display sizes

- Optional touchscreen, picture-in-picture video (PAL/NTSC)

- Video signal support includes: VGA, SOG, NTSC, RS170, PAL, S-video and DVI

- Compliance for shock (MIL-S-901D, Grade A), vibration (MIL-STD-167-1), EMI/EMC (MIL-STD-461E) and environmental (MIL-STD-810E)

- Anti-reflective and anit-glare coatings

- Field replaceable backlights and power supply

# Need A Harmonic Corrected DC Source from 3 phase ?

400 HZ Models 60 HZ

Wild Frequency

COTS

Modified

Custom

Abbott offers several models of Tranformer Rectifer Units (TRUs) which provide compliance to the various MIL-SPECs for EMI and harmonic suppression, including:

-MIL-STD 1399

-MIL-STD 704

-MIL-STD 461

-DO160

These power factor corrected units feature low parts counts for remarkably high MTBFs. Of course, they also meet the environmental MIL-SPECS which Abbott has focused on since 1961. Whether your application is in the air, land, or sea, we can provide you a solution for your front-end requirements.

Rock Solid Reliability

800-367-8200 www.abbottpower.com

#### Publisher

#### **PRESIDENT**

John Reardon, johnr@rtcgroup.com

Pete Yeatman, mail@yeatmangroup.com

#### **EDITORIAL DIRECTOR / Associate Publisher**

Warren Andrews, warrena@rtcgroup.com

#### **Editorial**

**EDITOR-IN-CHIEF**

Jeff Child, jeffc@rtcgroup.com

#### SENIOR EDITOR

Ann Thryft, annt@rtcgroup.com

#### CONTRIBUTING EDITOR

David Cotton, davidc@rtcgroup.com

#### **MANAGING EDITOR**

Marina Tringali, marinat@rtcgroup.com

#### CTACE EDITOD

Craig Choisser, craigc@rtcgroup.com

#### **COPY EDITOR**

Rochelle Cohn

#### Art/Production

#### CREATIVE DIRECTOR

Jenna Hazlett, jennah@rtcgroup.com

#### DESIGNER

Melissa Gaeta, melissag@rtcgroup.com

#### PRODUCTION DESIGNER

Kirsten Wyatt, kirstenw@rtcgroup.com

#### **DIRECTOR OF WEB DEVELOPMENT**

Jan Garcia, jang@rtcgroup.com

#### **WEB DEVELOPER**

Marke Hallowell, markeh@rtcgroup.com

#### <u>Advertising</u>

#### **CALIFORNIA COASTAL ADVERTISING MANAGER**

Diana Duke, dianad@rtcgroup.com (949) 226-2011

#### **WESTERN REGIONAL ADVERTISING MANAGER**

Lea Ramirez, lear@rtcgroup.com (949) 226-2026

#### **EASTERN REGIONAL ADVERTISING MANAGER**

Nancy Vanderslice, nancyv@rtcgroup.com (978) 443-2402

#### **EMEA SALES MANAGER**

Marina Tringali, marinat@rtcgroup.com (949) 226-2020

#### **BUSINESS DEVELOPMENT MANAGER**

John Koon, johnk@rtcgroup.com (858) 755-4999

#### BILLING

Maggie McAuley, maggiem@rtcgroup.com (949) 226-2024

#### COTS Journal

#### **HOME OFFICE**

The RTC Group, 905 Calle Amanecer, Suite 250, San Clemente, CA 92673 Phone: (949) 226-2000 Fax: (949) 226-2050, www.rtcgroup.com

#### **EDITORIAL OFFICES**

Warren Andrews, Editorial Director/Associate Publisher 39 Southport Cove, Bonita, FL 34134 Phone: (239) 992-4537 Fax: (239) 992-2396

Jeff Child, Editor-in-Chief

20A Northwest Blvd., PMB#137, Nashua, NH 03063

Phone: (603) 429-8301 Fax: (603) 424-8122

Ann Thryft, Senior Editor

15520 Big Basin Way, Boulder Creek, CA 95006

Phone: (831) 338-8228

#### Published by THE RTC GROUP

Copyright 2006, The RTC Group. Printed in the United States. All rights reserved. All related graphics are trademarks of The RTC Group. All other brand and product names are the property of their holders.

# We think inside the box ...

because outside, it can get pretty rough!

For more than 20 years, AP Labs has successfully leveraged design and manufacturing experience into system solutions that survive the harshest of environments.

Custom designs for backplanes, power systems and enclosures are possible with state-of-the-art tools, best-in-class components and quality manufacturing.

Be assured that our products specifications, warranty statements and service will exceed your expectations. Let our knowledgeable and responsive team of design and application engineers bring your project to a successful completion.

- ☑ Create Concept

- ☑ Leverage Experience

- ☑ Quality Manufacture

- ☑ Compliance Test

- Rugged Solution

www.aplabs.com rugged@aplabs.com 10864 Thornmint Road, San Diego, CA 92127

Phone: 800-822-7522

# Real teamwork means not getting in each other's way.

# So why aren't you working with Radstone?

Any group of individuals can claim to be a team. But a real team is motivated by a shared vision, a united purpose. A real team doesn't compete within itself: all of its members do what they do best at the right time and in the right place, their complementary skills harnessed in support of a common goal.

At Radstone, we don't just talk the talk. Real teamwork is our way of life – and for us, our customers are part of the team. When we win, our customers win. It's a game plan based on trust.

When it comes to mission-critical embedded computing solutions, Radstone teamwork delivers with maximum performance and minimum risk. That's why we're the team-mates of choice for some of the industry's biggest names.

Shouldn't you be working with Radstone?

Radstone. One team. One aim. One winning result.

# Inside Track

# AFRL Selects Mercury ARIES System for UAV Reconnaissance Program

The Air Force Research Lab (AFRL) at Wright-Patterson Air Force Base has selected Mercury Computer Systems to provide computer hardware and services for the Continuous Look Attack Management for Predator (CLAMP) Program. The goal of CLAMP is to develop and transition advanced sensor exploitation capabilities to the Long-Endurance Predator UAV (Figure 1).

CLAMP is the first U.S. Air Force program to undertake Mercury's ARIES (Airborne Reconnaissance Image Exploitation System) concept, in which airborne multi-sensor platforms will use stored sensor data for comparative purposes. ARIES is an adjunct processor that is designed to facilitate the migration of ground-based algorithms to the platform, adjacent to the sensor and with direct access to original sensor data, so that

image exploitation can occur in real time.

As the Predator UAV flies and collects data over a designated area for hours at a time, the multilook, multi-sensor nature of its mission can be fully exploited. By enabling the UAV to store, retrieve and process sensor data over a long period of time, warfighters will be able to detect changes in tactical conditions and allow them to pinpoint attacks or avoid dangerous situations.

In addition, CLAMP will combine other selected technologies in a systematic approach to enable the Predator UAV to fulfill its Hunter-Killer role with improved reliability and reduced collateral damage. Mercury plans to upgrade two MP-510 multiprocessor systems previously purchased by the AFRL, and to assist in the performance optimization of key applications to be tested by the CLAMP program.

Figure 1

The goal of the Continuous Look Attack Management for Predator (CLAMP) Program is to develop and transition advanced sensor exploitation capabilities to the Long-Endurance Predator UAV. The CLAMP system will enable the UAV to store, retrieve and process sensor data over a long period of time.

Mercury Computer Systems Chelmsford, MA. (978) 256-0052. [www.mc.com]. Saft America Cockeysville, MD. (410) 771-3200. [www.saftbatteries.com].

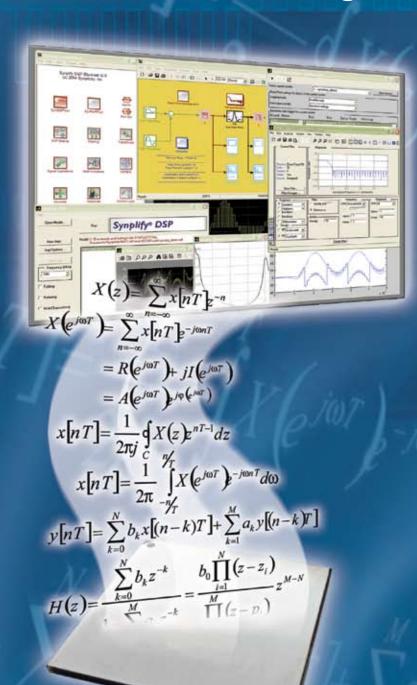

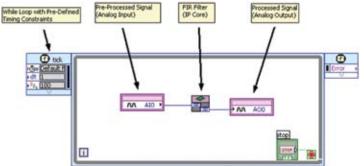

#### NCSA and SRC Computers Collaborate on Reconfigurable Computing Tools

SRC Computers, a manufacturer of reconfigurable computing systems, has entered into a joint development agreement with NCSA (National Center for Supercomputing Applications). Under the agreement NCSA will develop software and processes that will allow programmers in the embedded systems and signal processing communities to write programs using MATLAB/Simulink for use on SRC's reconfigurable computing systems. The result of the collaboration will describe in detail how to use the Mathwork's MATLAB/Simulink, Xilinx DSP System Generator and the SRC Carte programming environment macro capability to implement Simulink fixed-point designs on SRC's reconfigurable MAP processors.

#### EADS and Saft Team to Form U.S.-Based Thermal Battery Company

EADS and Saft America have inked a deal to form a new thermal battery subsidiary called Advanced Thermal Batteries Inc., located in Cockeysville, Maryland. This builds on the two firms' existing joint venture called ASB. ASB ranks as number one in Europe and number two worldwide in the thermal battery market, supplying thermal

batteries for missiles, launchers, aircraft, torpedoes and submarines. Thermal batteries are inert batteries designed for absolute reliability and shelf storage of at least 15 years. ASB, Saft America and EADS are merging their assets to offer both development and production capacities in the United States. Advanced Thermal Batteries Inc. supplies customized thermal batteries for missiles and smart weaponry.

The new subsidiary will provide to its American customers all the technologies that

have been proven by its parent companies. The new subsidiary, through ASB, already has sales in the American market, and hopes to become a leader in the thermal battery field in the United States.

EADS North America

Arlington, VA.

(703) 236-3300.

[www.northamerica.eads.net].

Get Connected with companies mentioned in this article. www.cotsjournalonline.com/getconnected

NCSA will be using SRC's newest portable MAPstation product (Figure 2) in its development work. Originally developed for the Air Force for use in mid-size UAVs, SRC's portable MAPstation is a compact general-purpose processor that typically performs operations such as radar processing, image processing and spectrum analysis 100 times faster than a microprocessor. NCSA will develop several digital signal processing applications for SRC's portable MAPstation to showcase the MATLAB/Simulink-to-MAP programming ability. One set of these applications will build on NCSA's earlier work in software-defined radio as part of the National Center for Advanced Secure Systems Research (www.ncassr. org) funded by the Office of Naval Research (ONR). Other applications for the portable MAPstation will include speech analysis and image processing. These applications will be ready for demonstration as early as Q4 2006.

The MathWorks

Natick, MA.

(508) 647-7000.

[www.mathworks.com].

SRC Computers

Colorado Springs, CO.

(719) 262-0213.

[www.srccomputers.com].

### CMC Selects Greenhills for Cockpit Avionics

CMC Electronics has selected the Green Hills Platform for Avionics with the INTEGRITY-178B RTOS to support the development of integrated cockpit avionics solutions. The RTOS will be used in the development

Figure 2

SRC's portable MAPstation is a compact general-processor system that typically performs operations such as radar processing, image processing and spectrum analysis 100 times faster than a microprocessor. The lightweight airborne enclosure weighs less than four pounds and has a maximum power consumption of 86W, 40W typical.

of a new CMC Electronics Aircraft Management System product line. The product supports an all-glass cockpit anchored by two powerful CMC Electronics Integrated Avionics Computers that are fully qualified to commercial standards. The rugged mission system uses a PowerPC 7457 processor and will support multiple display functions.

INTEGRITY-178B is a time and memory partitioned operating system, certified to DO-178B Level A with full ARINC-653-1 compliance. Support for ARINC-653-1 with its partitioning definition allows developers to deploy multiple applications on a single processor, at potentially multiple safety certification levels. That allows developers to reduce the number of onboard computers needed to support multiple software systems. The Platform for Avionics with INTEGRITY-178B is certified for multiple languages, including: Ada, C and Embedded C++.

Green Hills Software Santa Barbara, CA. (805) 965-6044. [www.ghs.com].

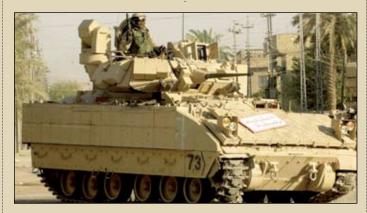

#### CPU Technology Gets Subcontract for Bradley Turent Drive PIB

BAE Systems has awarded CPU Technology a follow on production subcontract for

Bradley Combat Systems vehicle Turret Drive Position Interface Box (PIB) control systems. The new PIB systems will be installed in remanufactured and upgraded Bradley A3 Vehicles at BAE Systems in York, Pennsylvania. CPU Tech began providing the Bradley Position Interface Box two years ago with a modern System on Chip (SoC)-based PIB that is smaller, lighter, more reliable and lower cost than earlier systems.

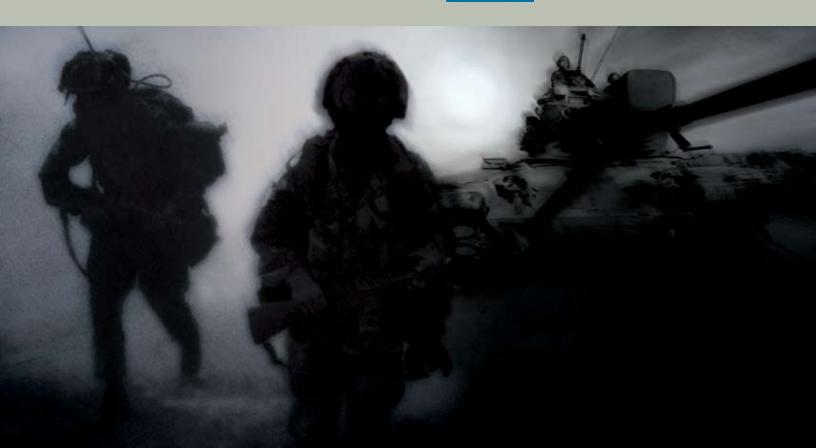

The Bradley A3 (Figure 3) features an advanced digital architecture that integrates communications equipment, digital sensors, battle management systems, embedded diagnostic and training systems. Last June, BAE Systems was awarded a series of delivery orders and contract modifications worth \$1.127 billion from the U.S. Army Tank-Automotive and Armaments Command (TACOM) to remanufacture and upgrade more than 500 Bradley Combat System vehicles.

CPU Technology Pleasanton, CA. (703) 251-2568. [www.cputech.com].

Figure 3

Shown here are soldiers in a Bradley armored vehicle assigned to the Oregon Army National Guard's Company C, 2nd Battalion, 162nd Infantry Regiment. The A3 upgrade version of the Bradley features an advanced digital architecture that integrates communications equipment, digital sensors, battle management systems, embedded diagnostic and training systems.

COTS Websites www.aaai.org

#### **Artificial Intelligence Site Provides Portal to All Things Al**

The DoD's interest and investment in autonomous vehicles—land, sea and air—continues to soar. As a result, interest in the science of artificial intelligence is moving into the foreground of military system designers. One source of such information is the American Association for Artificial Intelligence (AAAI), a nonprofit scientific society devoted to advancing the scientific understanding of the mechanisms underlying thought and intelligent behavior and their embodiment in machines. AAAI's goals

\*\*\* An extraction of the second plane of the s

AAAI's Web site provides a wealth of information about major AAAI activities such as conferences, symposia and workshops, and its books, proceedings and reports. The list of AI topics and subtopics on the site number in the hundreds, and the links to each topic page are listed alphabetically in an index list. Of particular interest is the topic page on Autonomous Vehicles, which in and of itself packs a wealth of information and links to related sites.

also include increasing public understanding of artificial intelligence, improving the teaching and training of AI practitioners, and providing guidance for research planners and funders concerning the importance and potential of current AI developments and future directions.

American Association for Artificial Intelligence, Menlo Park, CA. (650) 328-3123. [www.aaai.org].

# Perform like never before.

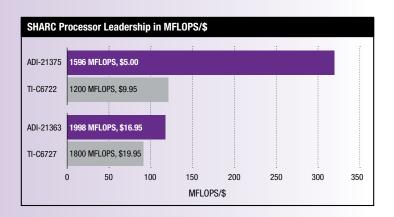

# From \$5 to 3.6 GFLOPS, your DSP job just got easier.

Worried about rounding errors in your 16-bit arithmetic? Anxious about noise in your frequency domain processing? What about blowing your project schedule as you move your floating-point concept to fixed-point implementation? Analog Devices SHARC® and TigerSHARC® Processors solve your most frustrating numeric DSP challenges. Now you can really perform.

For more than 10 years, SHARC has dominated the floating-point DSP market, delivering exceptional core and memory performance complemented by outstanding I/O throughput. At 319 MFLOPS per dollar, the SHARC family makes floating point more accessible than ever. And for high performance multiprocessing, TigerSHARC Processors deliver GFLOPS performance with glueless, 1 Gbyte/sec multiprocessing link ports, and 24 Mbits on-chip memory.

If you're ready to speed your time to market and showcase your design's real potential, Analog Devices SHARC and TigerSHARC Processors deliver floating-point performance—and performance density—like never before.

- "Floating-point processing essentially eliminates concerns about dynamic range and ensures precision in the most intensive and demanding signal processing tasks—but it's been an expensive alternative in terms of both cost and power. Architectural advances are now making this capability far more widely accessible."

- Dr. Alan Oppenheim

Ford Professor of Engineering

Massachusetts Institute of Technology

#### **SHARC Advantages**

- ► Broad portfolio of code- and pincompatible processors starting at \$5 and providing 2.4 GFLOPS of signal processing performance

- ► High precision computation enabled by SHARC's 32-bit fixedand floating-point architecture

- ▶ Up to 400 MHz core instruction rate

- ► Single-Instruction Multiple-Data (SIMD) computation architecture

- Simplified system design and lower system cost via a wide array of integrated peripherals

#### **TigerSHARC Advantages**

- ► Optimal balance of computational performance, large on-chip memory, and I/O bandwidth maximizes sustainable FFT performance

- ► Memory integration up to 24 Mbits accessible at core frequency enables internal execution of FFTs of 64 K points maximum

- Glueless, scalable multiprocessing capability with 5 Gbytes/sec aggregate throughput

- ► Interlocked pipeline for "out-of-the-box" execution of ported workstation code

- ➤ 24 Mbits of on-chip RAM three times more than the closest competition

#### Mackie TT24™ Digital Live Console

Mackie uses SHARC's on-board DSP power to provide audio dynamics, equalization, and effects processing in a way that's practical, intuitive, and fast enough for live sound.

#### **BMW M5 Series**

BMW chose SHARC Processors for control of its sophisticated 500 hp V-10 motor. The V-10 engine control unit performs an amazing 200 million calculations per second to ensure optimal performance.

#### R&S® Radio Communication Tester CMU With ADI floating-point processors,

Rohde & Schwarz provides a versatile mobile radio test platform that conforms to multiple international standards and delivers maximum measurement speed for extensive testing of current and future mobile radio networks.

#### iCyt™ Cell Separation Instrument

TigerSHARC Processors are used in a high throughput, biological cell separation instrument designed and built by iCyt Visionary Bioscience, Inc. while utilizing Bittware's TigerSHARC development boards.

Visit **www.analog.com/perform** for information on special bundled board offers from BittWare, Inc. and Analog Devices.

# **Main Feature**

Tailoring Processors for Military Applications

# Processors Combine Forces for Military Systems

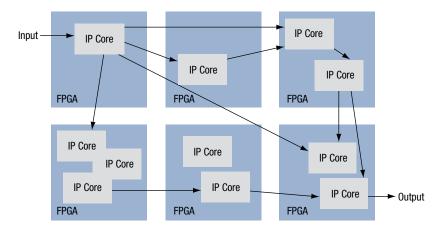

Next-generation, complex electronic defense systems often need multiple compute nodes. These are being supplied by multicore processors or by general-purpose processors in combination with FPGAs and/or DSPs.

Ann R. Thryft Senior Editor

hen it comes to the processors used in high-demand, complex compute-intensive military systems, the big news these days is the rise of FPGAs and the new generation of multicore processors.

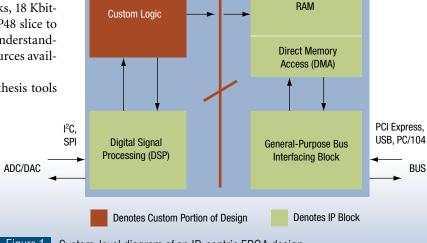

FPGAs are now big enough and powerful enough to take over an increasing number of digital processing tasks from general-purpose DSPs, or to work with them in the same design. Military engineers are using FPGAs as coprocessors that complement high-performance general-purpose processors (GPPs) for signal processing and sensor data processing, as well as image processing. FPGAs are found in an increasing number and type of defense systems, including submarine and ordnance detection, communications intercept and direction finding, for tanks, UAVs and helicopters (Figure 1).

FPGAs, DSPs and high-performance GPPs are being combined in military designs to provide the right kind of processing punch in the right place. For repetitive signal processing, encryption/decryption or beam-forming algorithms that require

Figure 1

Combinations of multiple processor such as general-purpose processors and FPGAs, are found in an ever increasing number of defense systems. The U.S. Navy's Airborne Laser Mine Detection System, used by pilots of H-60 helicopters, depends on this mix of processing power for processing signals and sensor data. Members of Explosive Ordnance Disposal Mobile Unit Eleven Detachment 9 fast rope from an SH-60F Seahawk helicopter assigned to Helicopter Anti-Submarine Squadron Two, during an air power demonstration in the South China Sea. (Photo by Photographer's Mate 3rd Class Jordon R. Beesley, courtesy of U.S. Navy.)

fast execution, FPGAs shine. In contrast to fixed processor architectures, they are flexible and scalable at multiple levels.

DSPs have been the processor of choice for applications requiring compute-intensive, high-speed calculations, since they can provide sustained, low-latency, high-throughput data processing. The benefits of DSPs include algorithmic capabilities optimized for fast floating-point math and programming with C. Applications that require different levels of processing will benefit from partitioning the design so it combines both FPGAs and DSPs.

Meanwhile, a new generation of multicore processors has appeared that will help improve the performance of next-generation electronic defense systems, such as radar, sonar, SIGINT and UAV control. Some of the most recent multicore architectures combine multiple cores of the same GPP on one chip so each core can run a separate program thread.

Mainstream processor vendors

Get Connected

with companies mentioned in this article.

www.cotsjournalonline.com/getconnected

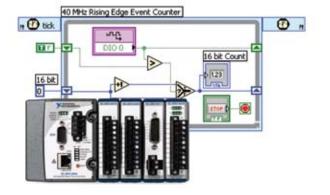

# Design to Deployment with One Graphical Environment

### **Design** with LabVIEW

Interactive algorithm design tools

Native simulation capabilities

Built-in analysis and I/O

## **Prototype** with LabVIEW

Reconfigurable FPGA I/O

COTS prototyping platform

### **Deploy** with LabVIEW

32-bit processor deployment

Same environment from algorithm design to implementation

### Graphical Development Platform for Design, Control, and Test

- Intuitive embedded programming representation

- Rapid application development

- Built-in I/O connectivity and ready-to-run analysis

Improve your productivity with LabVIEW graphical system design. View technical tutorials online at ni.com/labview/embedded.

(800) 890 6229

# FPGAs, DSPs and high-performance GPPs are being combined in military designs to provide the right kind of processing punch in the right place

such as Intel, AMD and Freescale are taking this symmetric multiprocessing approach to boost performance without burning huge amounts of power. For example, Intel's new dual-core technology the 2 GHz Intel Core Duo T2500/1.6 GHz Core Duo L2400—boasts almost twice the performance of Pentium processors in the same space, and with only slightly higher power consumption. Other dualcore designs include the Freescale 1.5 GHz 8641 PowerPC with its dual integrated 64-bit memory controllers, and AMD's 2.2 GHz 64-bit, dual-core, 30/55/95W Opteron. Quad core designs are also in the works.

Another type of multicore processor is the tiled design. There are several different versions. The Cell Broadband Engine processor, developed by IBM, Toshiba and Sony Group, includes eight identical, synergistic processing elements in addition to a core based on IBM's Power Architecture. Originally created for the video game market, the Cell processor's peak performance is more than 200 GFLOPS, or 200 billion FLOPS.

The 64-bit, 25 GFLOPS CSX600 is a multi-threaded array processor that acts as an accelerator and coprocessor. This tiled processor is offered by Clearspeed on a PCI-X add-on board.

A tiled processor under development by the Defense Advanced Research project (DARPA) is the Morphable Networked Micro-Architected (MON-ARCH) chip. This will unite two radically different architectures into a device that can act either as a single chip or as a system-on-chip.

## Intelligent Multifunction I/O Cards from North Atlantic Industries.

Function integration for reduced card count, weight, power, heat, and overall system cost.

- ~ Fill up to 6 slots per card with your choice of over 16 different function modules

- ~ **NEW!** Gigabit Ethernet Connectability

- ~ On-line Background Built-in-Test (BIT) alerts you of problems during operation

- ~ VME, cPCI, and PCI Platforms

- ~ Available as Conduction-Cooled/Wedge-Lock or Air-Cooled

- ~ Custom function designs

- ~ Can be configured with user definable FPGA

- ~ Extensive library of available functions

- ~ All major I/O Signal Types

To find out more about Intelligent Multifunction Cards, visit <a href="www.naii.com/multi">www.naii.com/multi</a> or call us at 631-567-1100 today.

Embedded Boards | Power Supplies | Instruments 631-567-1100 • Fax: 631-567-1823 • email: sales@naii.com

**SBS knows MIL-STD-1553.** For real time, deterministic systems, it's still the best option.

MIL-STD-1553 IS THE PREFERRED TECHNOLOGY for safety and

life critical applications because it outperforms the bleeding edge. There's no other solution that offers the same reliability levels for military, avionic and space applications, and that's why SBS offers a full range of superior 1553 hardware and software.

We offer our MIL-STD-1553 products in CompactPCI®, VME, PMC, PC-104, PCMCIA and PCI as part of our commitment to provide options to system designers. Many of our offerings are specifically designed and

tested to stand up to the demands of harsh environments that are common in defense and aerospace. Even now, we are designing and building rugged cards, boards and systems that will support 1553 into the next generation of land, sea and air platforms.

MIL-STD-1553 is a proven technology that has a distinguished record of service in extremely critical situations. MIL-STD-1553 may not be the "latest and greatest," but then again, sometimes the latest isn't the greatest.

1553-PMC3 1 to 4 MIL-STD-1553 channels for PMC

SBS knows.

Find the 1553 solution you're looking for at defense.sbs.com or call 800.SBS.EMBEDDED

# **Main Feature**

Tailoring Processors for Military Applications

# Commercial Processors in Military Applications

A wide variety of processor types is available for military applications. The use of a decision model can help narrow the choices for a given application type.

Dawn Levy, Senior Systems Application Engineer Stephen Pearce, Technical Director Mercury Computer Systems

types available today has significantly complicated the selection process for military imaging and signal processing applications. The various processor types range from FPGAs and DSPs to graphics processing units (GPUs) and single, vector and multicore processors.

This wide variety provides an opportunity to fine-tune hardware platform environments through an assessment of clear performance tradeoffs. Selecting the optimal processing environment to meet application requirements is critical in ensuring successful deployments, particularly in complex military environments.

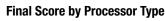

### Decision Model Criteria and Parameters

To simplify the selection process, a decision model can be developed with criteria such as bit resolution, software code type, field deployment requirements and applicability. This model can be used as a set of guidelines and includes parameters for, and a brief discussion of, each of these four decision criteria. It considers the fol-

lowing processor types: the Cell Broadband Engine (BE), GPUs, FPGAs, DSPs, PowerPCs (PPCs) and Pentiums.

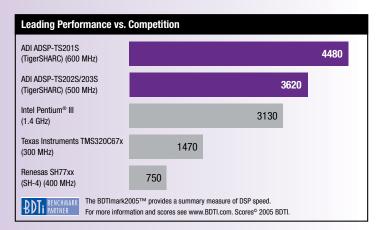

The model's parameters for the first criterion, bit resolution, include singlebit, 8- or 16-bit, floating-point and double precision. Certain processor types are clearly more adept at highprecision processing than others. With their math processing engines, the Cell BE, PPC and Pentium are most qualified for double-precision operations. However, FPGAs and DSPs most skillfully perform arbitrary low-precision arithmetic. GPUs, on the other hand, are great for 8-, 16- and 32-bit floating-point operations as long as the dataflow and

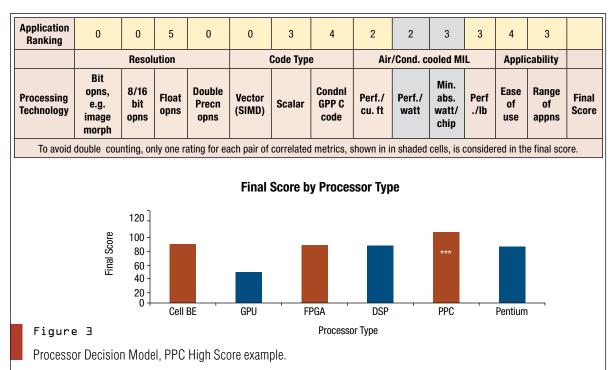

| Application<br>Ranking   | 0                                      | 0                   | 5             | 5                       | 4                | 3                  | 2                       | 5                | 5              | 4                             | 4            | 2                 | 2                    |                |

|--------------------------|----------------------------------------|---------------------|---------------|-------------------------|------------------|--------------------|-------------------------|------------------|----------------|-------------------------------|--------------|-------------------|----------------------|----------------|

|                          | Resolution                             |                     |               | Code Type Air           |                  | r/Cond. cooled MIL |                         | Applicability    |                |                               |              |                   |                      |                |

| Processing<br>Technology | Bit<br>opns,<br>e.g.<br>image<br>morph | 8/16<br>bit<br>opns | Float<br>opns | Double<br>Precn<br>opns | Vector<br>(SIMD) | Scalar             | CondnI<br>GPP C<br>code | Perf./<br>cu. ft | Perf./<br>watt | Min.<br>abs.<br>watt/<br>chip | Perf<br>./lb | Ease<br>of<br>use | Range<br>of<br>appns | Final<br>Score |

| Cell BE                  | 1                                      | 4                   | 6             | 6                       | 6                | 2                  | 2                       | 5                | 5              | 3                             | 3            | 4                 | 3                    | 145            |

| GPU                      | 2                                      | 2                   | 5             | 1                       | 6                | 1                  | 1                       | 4                | 4              | 2                             | 2            | 1                 | 1                    | 91             |

| FPGA                     | 6                                      | 6                   | 2             | 1                       | 5                | 6                  | 1                       | 6                | 6              | 6                             | 6            | 3                 | 4                    | 123            |

| DSP                      | 5                                      | 5                   | 3             | 1                       | 3                | 5                  | 4                       | 2                | 2              | 5                             | 5            | 4                 | 2                    | 97             |

| PPC                      | 4                                      | 3                   | 4             | 5                       | 4                | 3                  | 5                       | 3                | 3              | 4                             | 4            | 5                 | 6                    | 133            |

| Pentium                  | 3                                      | 1                   | 1             | 4                       | 1                | 4                  | 6                       | 1                | 1              | 1                             | 1            | 6                 | 5                    | 84             |

To avoid double counting, only one rating for each pair of correlated metrics, shown in in shaded cells, is considered in the final score.

Figure 1

Processor Decision Model, Cell BE High Score example. The model's top row, highlighted in yellow, depicts application characteristics that are ranked from lowest to highest importance using a score of 0 to 5. At the bottom, the rank order from highest to lowest final scores across all processor types is shown as bar height in the graph.

processing types closely match their internal architecture, which is optimized for visualization.

The second criterion, software code type, characterizes application logic. Model parameters include vector single-instruction-multiple-data (SIMD) processing, scalar code and conditional, "if-then-else" general-purpose programming (GPP) C code.

Whereas the Pentium or PPC are best suited for conditional C code, the repetitive nature of vector processing lends itself best to the Cell BE, GPU or FPGA. FPGAs do very well when an algorithm must access its data in an order that is cache-unfriendly. For cache-friendly data access, a

processor is often preferred. However, even in these cases an FPGA might still be the best choice if it is needed to get sensor I/O data into a system, because engineers might face the choice of adding a processor or just deploying a bigger FPGA for the I/O task.

GPUs excel when the algorithm happens to match the GPU architecture. This architecture is highly tuned to streaming matrix operations with moderately complex data structures, little conditional code and little data reuse. Data re-sampling is a GPU forte. To program a GPU, however, requires specialized training in graphics terminology.

DSPs excel in places where their instruction sets fit the application. They can

handle some conditional C code. In some applications, they can provide close to the sort of performance one might expect from an FPGA. They thus occupy the middle ground between GPPs and more application-specific processing elements.

The third criterion, deployed environment, refers to requirements for ruggedization, such as air-cooled or conduction-cooled military environments. The model considers two basic parameters: performance per cubic foot and performance per pound.

Processors that perform well per cubic foot also achieve relatively

strong performance per watt. Similarly, good performance per pound is typically a result of the chip's power efficiency, or minimum absolute watt per chip. To avoid double counting, however, only one rating for each pair of correlated metrics is considered in the model's final score.

In environments where weight is a critical concern, such as airborne platforms, devices that provide processing at the lowest absolute power per chip, such as DSPs and PPCs, are good candidates. In situations where the parallelism of an FPGA can be effectively exploited, the processing element's higher power

# **Need Military Gigabit Ethernet?**

### ET-71000 GigEXTREME™ TCP/IP Offload Engine

|                                                     | GigEXTREME™ | Other TOE Cards | NICs with Partial<br>Offload |

|-----------------------------------------------------|-------------|-----------------|------------------------------|

| Processor Loading*                                  | 5%          | 5%              | 50% to 70%                   |

| RTOS Support                                        | ✓           | <b>✓</b>        | _                            |

| No Application Modification or Recompilation Needed | <b>✓</b>    | _               | <b>✓</b>                     |

| No Use of Upscreened<br>Commercial Components       | ✓           | _               | -                            |

| Military Rugged                                     | <b>✓</b>    | Some            | Some                         |

| IPv6 Capable                                        | <b>✓</b>    | _               | _                            |

<sup>\*</sup> Processor loading measured for the TCP/IP receive network task on a 1 GHz Power PC® host.

Toll Free: 1-800-DDC-5757 Web: www.ddc-web.com E-mail: info@ddc-web.com

EVRISE powergroup of companies

military aerospace

transportation telecommunication

Civil Aerospace DO-160 **Custom Military Power Supplies** Mil -Std 704, 461, 810 **VME Power Supplies**

www.pascall.co.uk

**Custom Military Power Supplies** Mil -Std 704, 461, 810 Harsh Environments Configured Module Systems

www.xcelpower.com

**RO** Associates

50-1000W COTS Modules Standard Products **DC-DC Converters** PFC front end Modules

www.roassoc.com

Power of 3

Companies are subsidiaries of **EMRISE** Corporation, Rancho Cucamonga, CA 91730

consumption is offset by its higher performance.

Interestingly, where performance per cubic foot is more important, it is the processingper-watt metric of the processing element that most effectively helps solve the problem. Therefore, FPGAs, Cell BEs and GPUs are the most suitable in space-constrained environments such as ground-based vehicles.

The fourth criterion, applicability, encompasses both the range of

applications that can be supported on the processor and the processor's ease of use. It compares these parameters against the needs of those applications for which each processing element is most suitable. The ease-of-use parameter does not consider any specialized skillsets an organization may possess.

In this category, PPCs and Pentiums rank highest, since design engineers in nearly all organizations use at least one of these processors. In contrast, there are significant challenges in leveraging GPUs for military applications. The most significant are device drivers for non-x86 hosts and operating systems that are not Windows or mainstream Linux implementations on the x86. FPGAs are becoming more widely applicable here, while DSPs remain chiefly specific to application type. The Cell BE holds promise for a reasonably wide range of processing requirements where a lot of DSP and some general-purpose processing are required.

#### **Processor Tradeoffs**

Using the model, subjective capability ratings are assigned to each processor type for each decision parameter. In any given category, these ratings are scored from a low of 1 to a high of 6. Application characteristics are ranked from lowest to highest importance using a score of 0 to

5. Although individual model values are debatable, the aggregate result, or final score, proves useful in determining the optimal processor choice for the application, or part thereof, being assessed.

The final score is computed as the sum

of the individual parameters weighted by the application rankings. For example, the final score of 145 for the Cell BE High Score example (Figure 1) was derived as shown:  $\{(0^*1) + (0^*4) + (5^*6) + (5^*6) + (4^*6) + (3^*2) + (2^*2) + (5^*5) + (4^*3) + (2^*4) + (2^*3) = 145\}.$

Although final scores can be presented graphically, it is the ranking order from highest to lowest across all of the processor types that proves most useful to the difficult problem of prioritizing processor

choices. Relative scores are less meaningful because they are not used in the assessment of each processor type against the specific criteria. When implemented as an Excel spreadsheet, the rank ordering of processors adjusts automatically to a score that indicates the order needed to consider each different processor type as a system solution to the application problem.

In the Cell BE High Score example (Figure 1), the specific application description exemplified in its high processing

score contains significant floating-point and double-precision operations, indicative of radar or beam-forming applications. Moreover, the application contains a combination of vector, scalar and conditional "C" programming components. This particular application also requires strong performance per cubic foot as well as per pound, typically required for military airborne deployed systems. The applicability criterion is of limited importance in this case, which is to be expected of mission-specific systems.

Use of the model illustrates that the Cell BE, closely followed by PPCs and FPGAs, is most suitable for computationally intensive, high-precision, space-constrained, deployed applications.

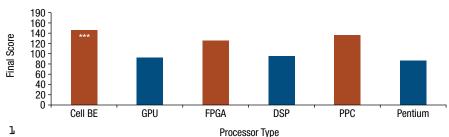

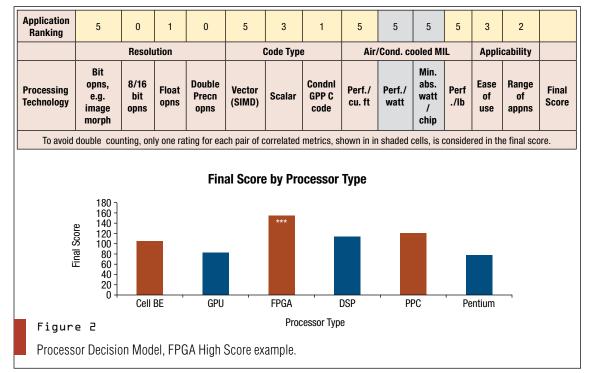

In the second FPGA High Score example (Figure 2), a bit operation application with vector arithmetic favors an FPGA implementation, closely followed by the PPC. Here, size, power and weight are of critical importance. This application could be an image formation processing system that is co-located at the sensor in a manned or unmanned airborne platform. As sensor data continues to overwhelm satellite data links, the ability to process in real time close to the sensor is critical.

A very different set of issues is posed by a floating-point application that incorporates both scalar and conditional "C" code. In this PPC High Score example (Figure 3), size, weight and power management are of moderate concern, but applicability is important. In this case, the model suggests that the PPC be considered first.

This could be a target-recognition, tracking, or other rule-based system that requires some flexibility. Ideally, such post-processing applications would coexist with the sensor and image processor, as hosting algorithms on deployable platforms in lieu of in-ground stations would further empower warfighters with real-time intelligence. The integration of new algorithms with embedded high-performance computers is the key enabler for this real-time capability.

Mercury Computer Systems, Inc. Chelmsford, MA. (978) 256-1300. [www.mc.com].

# True -55°C to +85°C operation... Standard!

Aitech continues to provide industry standard open systems architectures such as VMEbus and CompactPCI products, designed and tested to -55°C to +85°C as standard, because you can't bypass the rules of engagement either.

We can't change the physics... but we can ensure your COTS sub-systems are designed, built, and tested to perform reliably at the temperature extremes of your specification – without custom development, "work-arounds", or compromises.

We take the extra steps... including pre-screened parts qualification, HALT, and 100% HASS/ESS testing to ensure that every standard Aitech product meets all your temperature and rugged performance specifications...standard.

We've been there... Aitech subsystems have been proven in the world's most demanding mission-critical mil/aero applications – from complex ground, air and sea platforms to rad-tolerant solutions for the Space Shuttle, International Space Station and now earth orbiting satellites!

We've done that... Meeting full temperature-range specifications with standard products is just part of our 20+ year heritage and commitment to COTS advancements – from the first conduction-cooled Mil-Spec VME board in 1984, to today's highest functionality MIPS/Watt boards, multi-Gigabyte mass Flash mass memory cards, and high-speed mezzanines.

We have the proof...Visit our web site or call for more information and our catalog of proven solutions.

Aitech Defense Systems, Inc. 9301 Oakdale Avenue Chatsworth, CA 91311 email: sales@rugged.com Toll Free: 888-Aitech8 - (888) 248-3248 Fax: (818) 718-9787

www.rugged.com

# Ready!

Design with Quartus II development tools.

Set!

Prototype with Stratix" II FPGAs.

# Go to Market!

Ramp to production with Stratix II FPGAs or migrate seamlessly to HardCopy\* II structured ASICs.

The quickest & easiest path to production.

The Programmable Solutions Company®

www.altera.com

Technobox produces custom and off-the-shelf PMCs.

Our extensive range of solutions includes versatile FPGA-based digital I/O, async I/O, SATA, Ethernet, and IDE controllers. Plus a variety of adapters, extenders, and tools for PMC development or integration.

Make us your first stop for PMC Solutions.

www.technobox.com

Digital I/O

CompactFlash

Fast/Wide

**PrPMC**

PMC-to-PCI

Your Source for PMCs, Adapters, and Tools.

RS-232/422/485

LVD/SE

PIM

PMC-X

Test Access & Bus Analysis

**Carriers**

Extenders

140 Mount Holly Bypass - Unit 1 Lumberton, NJ 08048 Tel. 609-267-8988 Fax 609-261-1011

# Changing Horses in Midstream: Partial Reconfiguration for FPGA Designs

The ability to leverage partial reconfiguration for programmable logic opens new doors to a whole host of applications such as software defined radio, dynamic instruction set computing and automatic target recognition.

by Mark Goosman Xilinx

ngoing trends in logic design such as shorter product lifecycles, greater design complexity and increased scaling (e.g., "Moore's Law") are adding increasing pressure for faster design speed and lower power in a smaller physical space. Although today's advanced FPGAs are rapidly evolving to address these issues of speed, power and size, new technologies in the area of partial reconfiguration offer the promise of even greater advances.

Partial reconfiguration is a design process that allows a limited, predefined portion of an FPGA to be reconfigured while the remainder of the device continues to operate. This is especially valuable where devices operate in a mission-critical environment and cannot be disrupted while subsystems are redefined. The ability to partially reconfigure a device takes the already powerful benefits of reprogrammability to a much higher level.

The obvious benefit of reconfigurable devices, such as FPGAs, is that the functionality with which a device is configured can be changed and updated at some time in the future. As additional functionality is available or design improvements are made available, the FPGA can be shut down, completely reprogrammed with new logic and operations can be resumed. Partial reconfigurability addresses the environment where logic needs to be changed or updated within a part of an FPGA without disrupting the entire system. This may be a design comprised of several blocks of logic and, without disrupting the system and stopping the flow of data, requires an update of the functionality within one block.

Using partial reconfiguration, designers can dramatically increase the functionality of a single FPGA, allowing for fewer,

smaller devices than would otherwise be needed. This allows for additional functionality, lower power, reduced cost and less physical space on the board.

Partial reconfiguration is useful for systems with multiple functions that can time-share the same FPGA device resources. In such systems, one section of the FPGA continues to operate while other sections of the FPGA are disabled and reconfigured to provide new functionality. This allows concurrent support for multiple independent applications in a single FPGA. This is somewhat analogous to dynamic task switching or multitasking of a general-purpose processor. Without this capability, it would be necessary to reconfigure the entire FPGA to support a different application, which would result in the loss of all previous applications.

Partial reconfiguration provides an advantage over multiple full bit streams in applications that require continuous operation, which is not otherwise accessible during full reconfiguration. One example is a graphics display that utilizes horizontal and vertical synchronization. Because of the environment in which this application operates, signals from radio and video links need to be preserved—but the format and data processing format may require updates and changes during operation. With partial reconfiguration, the system can maintain these real-time links while other modules within the FPGA are changed on-the-fly.

In order to implement partial reconfiguration on an FPGA, it first requires an FPGA that inherently supports the dynamic

Get Connected with companies mentioned in this article. www.rtcmagazine.com/getconnected

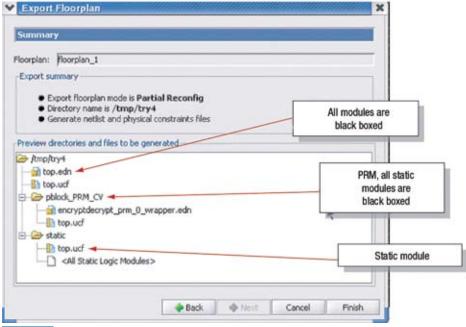

Figure 1 All static logic is grouped in a single Pblock AG\_base.

reconfiguration of only portions of the device, while leaving the other portions unaffected. Then a set of software development tools are needed that support the development of applications restricted to boundaries that comply with the hardware architecture of the FPGA. Finally, some form of basic controller must be available to dynamically manage the reconfiguration of the FPGA. This could be an embedded general-purpose processor (GPP), a soft core GPP, or an external GPP connected to the FPGA. In this shared resources model, the same embedded GPP that is running the design infrastructure and operating environment is also managing the partial reconfiguration of the FPGAs.

In an FPGA, all user-programmable features are controlled by memory cells that are volatile and must be configured on power-up. These memory cells are known as the configuration memory, and define the look-up table (LUT) equations, signal routing, input/output block (IOB) voltage standards and all other aspects of the design.

PRM1... PRMn Static I0 buffers, clock logic and bus macros

Figure 2 The hierarchy for a partial reconfiguration design.

To program configuration memory, instructions for the configuration control logic and data for the configuration memory are provided in the form of a bitstream, which is delivered to the device through the JTAG, SelectMAP, serial, or ICAP configuration interface.

Typically, a user performs the initial programming by downloading an entire bitstream to an inactive target device. Using partial reconfiguration, a subset of the FPGA can be reprogrammed using a partial bitstream. You can use partial bitstream to change the structure of one part of an FPGA design as the rest of the active device continues to operate.

#### A Methodology for Partial Reconfiguration

Successful implementation of a design using a partially reconfigurable flow requires following a strict design methodology. A reconfigurable design will consist of partially reconfigurable modules (PRMs) that will be swapped in and out of the FPGA and the static logic, which will remain in place. The general picture of the design flow involves the need to insert bus macros between the PRMs and the rest of the design, the static or fixed logic that remains in place. Bus macros are the channels or ports through which modules communicate and pass data. This allows a fixed communication channel for the static logic regardless of the reconfigurable logic on the other side.

Successful design requires following the guidelines of the synthesis tools to generate a partially reconfigurable net list. The synthesis tool must be configured so that no optimizations occur across hierarchical boundaries. This is generally done with a KEEP\_HIERARCHY or similar directive.

The next step is to use the tool to floorplan the PRMs and cluster all static modules together and then place the bus macros between the PRMs and the static logic following PRM-specific design rules. Finally, run the partial reconfiguration implementation flow

PlanAhead 8.1 from Xilinx is an example of a single environment (or platform) used to manage the preceding guidelines, which can be broken down into the following steps:

- 1. Net list import

- 2. Floorplanning the design for partial reconfiguration

- 3. Design rule checks

- 4. Net list export

- 5. Implementation flow management

- 6. Bitstream size estimation

Although these steps are straightforward, the methodology requires meticulous implementation in order to ensure success. Changing out a portion of a complex, high-speed design does not allow much margin for error.

Use a tool like PlanAhead that works with imported net lists, such as those

from XST or Synplify, to import any hierarchical net list (single edf/ngc or multiple edf/ngc files). Then follow the regular guidelines to import the design into the tool and create a floorplan as you would with any non-partially reconfigurable design.

Floorplaning for partial reconfiguration is an important step in the partial reconfiguration flow. Floorplanning is based on design partitions referred to as physical blocks, or Pblocks. A Pblock can have an area (such as a rectangle) defined on the FPGA device to constrain the logic. The designer can define Pblocks without rectangles and the implementation software will attempt to

group the logic during placement. Net list logic placed inside of Pblocks will receive AREA\_GROUP constraints.

Floorplanning for partial reconfiguration entails several key subtasks. The first subtask is to assign an area for the PRM by creating a Pblock with an area defined within the fabric. This includes assigning the values for RANGES for the Pblock. The MODE constraint must be defined for all reconfigurable regions (MODE=RECONFIG). This constraint prevents the implementation tools from failing with unexpanded block errors during implementation of the static and reconfigurable modules.

Every top-level module, other than PRMs, should be grouped together in a single Pblock. This is called a static logic block. This block should not have a RANGE defined; this will cluster the static logic together in a single Pblock. Select all top-level modules (except the PRMs) and assign them to a Pblock. Figure 1 shows the static logic grouped in a Pblock named AG\_base. When the floorplanning is completed in the design tools, the resulting physical hierarchy will be organized as shown in Figure 2.

The next step is to place the bus macros. Bus macros are physical ports that connect a PRM to static logic. Any connection from a PRM to static logic should always go through a bus macro. Bus macros are instantiated as black boxes in RTL and are filled with a predefined routing macro in the form of an .nmc file. Bus macros are placed on the PRM boundary. Static logic connected to PRMs will migrate toward the bus macro during placement.

Given the complexity of the flow, it is very common for mistakes to be introduced in the original RTL and during the floor-planning process. Any tool worth its salt will check for design violations. Also integrated into this feature, in the case of PlanAhead is the PR-Advisor, which provides feedback on how to improve your design. There are a number of design rule checks that are specific to Partial Reconfiguration.

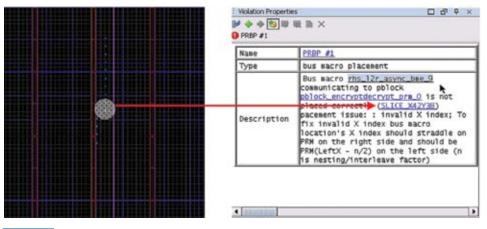

The bus macro DRC provides verification for all design rules related to bus macro connectivity and placement. One example

Figure 3 The PRBP DRC verifies all rules that should be followed for bus macro placement.

Figure 4 Special consideration should be given to timing-critical paths, which include an asynchronous path.

of a bus macro DRC is the PRBP check. This DRC checks for all rules that should be followed for bus macro placement. Figure 3 shows an example of a design that failed the PRBP DRC. In this case, the tool tells us that the interleaved/nested macro should be placed at SLICE\_X41Y.

The Floorplanning DRC covers floorplanning rules. Clock objects (global clock buffers, DCM) and I/Os should be placed and static logic clustered. The glitching logic DRC verifies glitching logic elements (SRL and distributed RAM) above and below PRM regions.

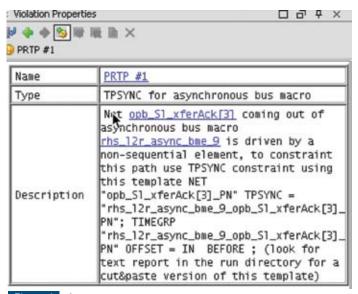

Another DRC is the timing advisor/DRC. This provides a check for timing-related issues. One example of timing DRC is the PRTB check. With the PRTB check, the static module is implemented before the PRM during the implementation phase. Regular timing constraints do not cover the paths that cross between the static and a PRM module. This does not

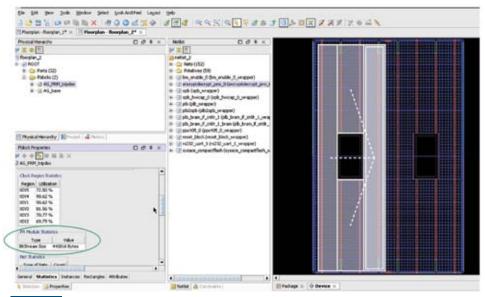

Figure 5 Upon successful completion of the floorplanning DRC processes, all modules will be displayed in black text within the Export Floorplan dialog box.

Figure 6 The display of Pblock properties includes the estimated size of the bitstream.

present a problem, provided that the bus macro is synchronous. However, if it is an asynchronous bus macro, the static module does not know about the propagating of asynchronous paths, as shown in the example in Figure 4. This could be important if these paths are timing-critical. One way to pass this information to the static module is to specify a TPSYNC constraint on the bus macro output net. PlanAhead software will recommend a TPSYNC constraint that can be added to the .UCF file.

Once the design is floorplanned and passes the DRC checker, it is ready to be exported. The design tools should take care of exporting the original hierarchical net list into a PR-style net list that has a specific format (static and PRM in separate directories). The export directory will appear as shown in Figure 5. Next, a partial reconfiguration flow wizard, shown in Figure 6, runs the partial reconfiguration implementation on the exported design. It will produce a full bitstream for the complete design and a partial bitstream for each of the PRMs. The implementation steps are:

- Initial budgeting

- Static module implementation

- PRM module implementation (one implementation for each version of every PRM)

- Assembly and bitstream generation (results are stored in the merge directory)

The Pblock statistics report includes a section that reports PRM bitstream size (Figure 6). This information can be used for estimating the size of configuration memory storage such as external flash and DDR. This information can also be used to calculate how long it will take to swap the module based on your bitstream memory interface.

Partial reconfiguration offers a tremendous opportunity for designers looking for a way to increase the functionality of their design, achieve lower power and reduce the number of devices on their board. Using new design tools and techniques becoming available for partial reconfiguration applications can greatly simplify the complexities of juggling the dynamic operating environment of these cutting-edge applications, allowing a single device to operate in applications that previously

required multiple FPGAs along with the required power, board space and design overhead.  $\square$

Xilinx San Jose, CA. (408) 559-7778. [www.xilinx.com].

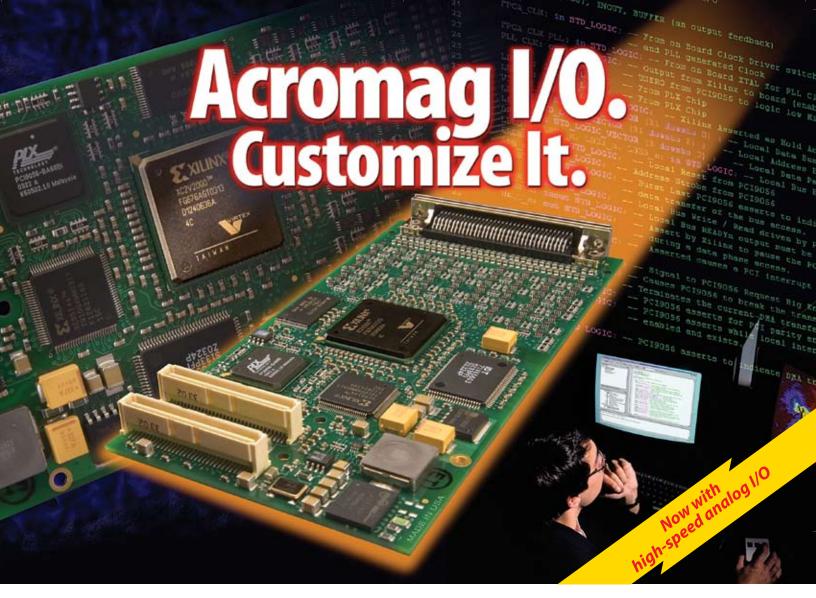

### Acromag introduces affordable FPGA I/O. For ALL your projects.

s an engineer, your projects are unique, ever-changing, and budget-bound. That's why our new PMC modules give you an affordable solution to create custom I/O boards.

But if you thought FPGA computing was only for top-end applications, think again. Our PMCs are ideal for protocol conversion, simulation, in-circuit testing, and much more. So why settle for generic I/O when you can design exactly what you need while staying in budget and reducing your time to market?

- Virtex®-II FPGA with 500K, 2M or 3M system gates

- 1Mb on-chip RAM, 9Mb on-board SRAM

- Fast PCI with 32-bit, 66MHz dual DMA

#### Cost-effective custom I/O

Choose from a variety of I/O configurations:

- Digital I/O:TTL, RS422, or LVDS I/O

- Analog I/O: four 20 or 65MHz A/D and two D/A

#### Faster time to market

Why waste precious time building a board from scratch? Our new FPGA modules let you process your I/O signals any way you want. Quickly.

#### Flexibility to meet unexpected challenges

Acromag FPGA I/O will help you bring your projects in on time and under budget. And with

FPGAs, you'll be ready to adapt to all the inevitable changes.

Thinking about FPGA I/O?

Think flexible. Think affordable.

Think Acromag.

www.acromag.com 800-881-0268 or 248-624-1541

Industry Pack FPGA I/O also available

# Reduce Cost, Risk and Time-to-Market with an FPGA-to-Structured ASIC Strategy

The costs, development times and risks of ASIC designs have become all but prohibitive. Finalizing a design on an FPGA and moving it to a structured ASIC can cut cost, time and risk as well as result in smaller size and lower power consumption.

by Danny Biran Altera

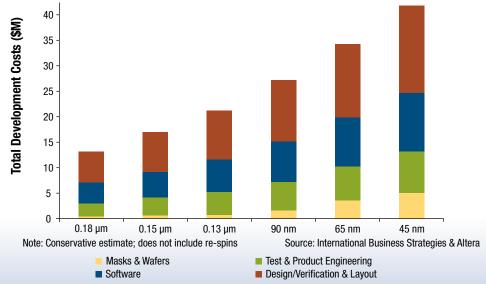

ew would argue that ASICs and ASSPs have become viable vehicles for only a few silicon vendors. As process nodes continue to shrink—to 90 nm now and to 65 nm in the near future—not many vendors are willing to take on the risk associated with an ASIC design unless they have a very high level of confidence that their chip will be sold in huge volumes to justify an investment that is often tens of millions of dollars (Figure 1). ASICs are under pressure. It is increasingly difficult for companies to justify the development of a new chip with the very

high NRE price tags. If chip development cost is \$30M, R&D costs are 20% of revenue, and one expects 10% market share, only a \$1.5 billion market opportunity can justify the expense. There aren't many markets of this size that can be serviced with a single product.

One of the risks associated with building an ASIC is that its functionality is fixed during fabrication, resulting in the need to "get it right the first time," which can often be hard to achieve. The cost of redesign for even a small portion of an ASIC that

doesn't work may be prohibitive in terms of both time and money. To mitigate this risk, FPGAs are often used as prototyping vehicles. With their high levels of logic density and performance, high-density FPGAs help developers implement complex designs that can be tested in the target system. FPGA prototypes offer many distinct advantages, allowing a design to have its hardware, application software and firmware fully developed and tested at full speed without a multi-million-dollar price tag.

Figure 1 The cost of chip development goes up dramatically as technology nodes shrink.

#### Moving to a Structured ASIC

Once the design is prototyped in the FPGA, the next step is to move to an effective silicon platform. Migrating from an FPGA to an ASIC is tricky and time-consuming, since there is generally a good

deal of work required to make sure the original design will still function correctly when implemented as an ASIC.

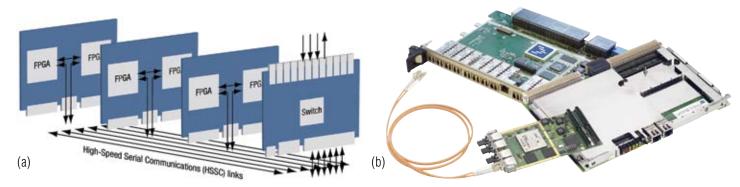

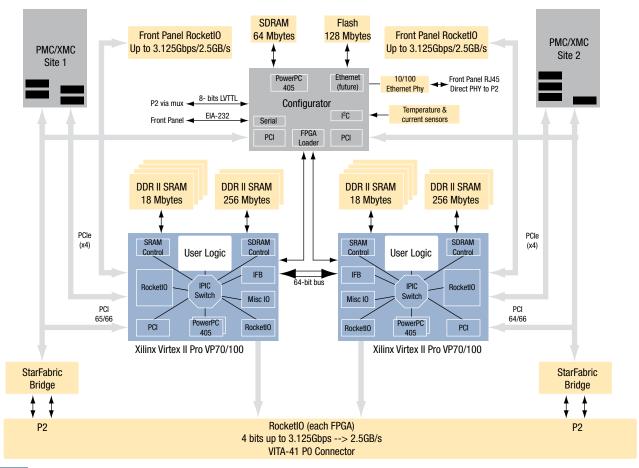

A better solution is to move the verified FPGA design onto a structured ASIC, which has the characteristics of an FPGA and most attributes of an ASIC, and is significantly smaller than an FPGA. A structured ASIC has near-ASIC performance and power consumption, along with a shorter development cycle and lower NRE than an ASIC. However, it has a much lower unit cost than a comparable FPGA—as much as one-tenth the cost.